# Four-Bit Single-Chip Microcontrollers with 8, 12, and 16 KB of On-Chip ROM

#### Overview

The LC662516A, LC662512A, and LC662508A are 4-bit CMOS microcontrollers that integrate on a single chip all the functions required in a special-purpose telephone controller, including ROM, RAM, I/O ports, a serial interface, a DTMF generator, timers, and interrupt functions. These microcontrollers are available in a 64-pin package.

#### **Features and Functions**

- On-chip ROM capacities of 8, 12, and 16 kilobytes, and an on-chip RAM capacity of 512 × 4 bits.

- Fully supports the LC66000 Series common instruction set (128 instructions).

- I/O ports: 58 pins

- · DTMF generator

- This microcontroller incorporates a circuit that can generate two sine wave outputs, DTMF output, or a melody output for software applications.

- 8-bit serial interface: Two-wire interface (16-bit data length. Supports cascade connection.)

- Instruction cycle time: 0.95 to  $10 \mu s$  (at 3.0 to 5.5 V)

- Powerful timer functions and prescalers

- Time limit timer, event counter, pulse width measurement, and square wave output using a 12-bit timer.

- Time limit timer, event counter, PWM output, and square wave output using an 8-bit timer.

- Time base function using a 12-bit prescaler.

- Powerful interrupt system with 11 interrupt factors and 8 interrupt vector locations.

- External interrupts: 3 factors/3 vector locations

- Internal interrupts: 8 factors/5 vector locations

(Waveform output internal interrupts: 3 factors and 1 vector; shared with external expansion interrupts)

- Flexible I/O functions

Selectable options include 20mA drive outputs, inverter circuits, pull-up and open drain circuits.

- Optional runaway detection function (watchdog timer)

- 8-bit I/O functions

- Power saving functions using halt and hold modes.

- Packages: DIP64S, QIP64E (QFP64E)

- Evaluation ICs: LC665099 (evaluation chip) + EVA86K-ECB662500 LC66E2516(on-chip EPROM microcontroller)

- Any and all SANYO products described or contained herein do not have specifications that can handle applications that require extremely high levels of reliability, such as life-support systems, aircraft's control systems, or other applications whose failure can be reasonably expected to result in serious physical and/or material damage. Consult with your SANYO representative nearest you before using any SANYO products described or contained herein in such applications.

- SANYO assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all SANYO products described or contained berein

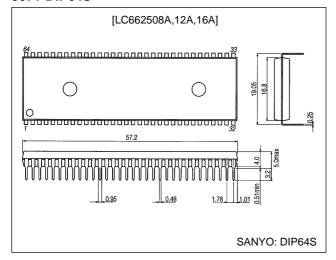

# **Package Dimensions**

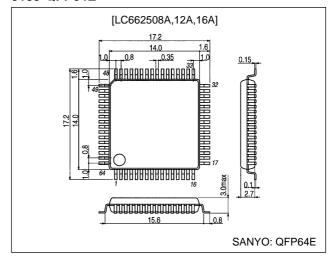

unit: mm

## 3071-DIP64S

# unit: mm **3159-QFP64E**

## **Series Organization**

| Type No.                  | No. of pins | ROM capacity           | RAM capacity | Pa                    | ckage                | Features                                             |  |

|---------------------------|-------------|------------------------|--------------|-----------------------|----------------------|------------------------------------------------------|--|

| LC66304A/306A/308A        | 42          | 4 K/6 K/8 KB           | 512 W        | DIP42S                | QFP48E               |                                                      |  |

| LC66404A/406A/408A        | 42          | 4 K/6 K/8 KB           | 512 W        | DIP42S                | QFP48E               | Normal versions                                      |  |

| LC66506B/508B/512B/516B   | 64          | 6 K/8 K/12 K/16 KB     | 512 W        | DIP64S                | QFP64A               | 4.0 to 6.0 V/0.92 μs                                 |  |

| LC66354A/356A/358A        | 42          | 4 K/6 K/8 KB           | 512 W        | DIP42S                | QFP48E               |                                                      |  |

| LC66354S/356S/358S        | 42          | 4 K/6 K/8 KB           | 512 W        |                       | QFP44M               | Low-voltage versions                                 |  |

| LC66556A/558A/562A/566A   | 64          | 6 K/8 K/12 K/16 KB     | 512 W        | DIP64S                | QFP64E               | - 2.2 to 5.5 V/3.92 μs                               |  |

| LC66354B/356B/358B        | 42          | 4 K/6 K/8 KB           | 512 W        | DIP42S                | QFP48E               | Low-voltage high-speed versions                      |  |

| LC66556B/558B/562B/566B   | 64          | 6 K/8 K/12 K/16 KB     | 512 W        | DIP64S                | QFP64E               | 3.0 to 5.5 V/0.92 μs                                 |  |

| LC66354C/356C/358C        | 42          | 4 K/6 K/8 KB           | 512 W        | DIP42S                | QFP48E               | 2.5 to 5.5 V/0.92 μs                                 |  |

| LC662104A/06A/08A         | 30          | 4 K/6 K/8 KB           | 384 W        | DIP30SD               | MFP30S               |                                                      |  |

| LC662304A/06A/08A/12A/16A | 42          | 4 K/6 K/8 K/12 K/16 KB | 512 W        | DIP42S                | QFP48E               | On-chip DTMF generator versions 3.0 to 5.5 V/0.95 µs |  |

| LC662508A/12A/16A         | 64          | 8 K/12 K/16 KB         | 512 W        | DIP64S                | QFP64E               | σ.ο το σ.σ ν/ο.9σ μα                                 |  |

| LC665304A/06A/08A/12A/16A | 48          | 4 K/6 K/8 K/12 K/16 KB | 512 W        | DIP48S                | QFP48E               | Dual oscillator support<br>3.0 to 5.5 V/0.95 µs      |  |

| LC66E308                  | 42          | EPROM 8 KB             | 512 W        | DIC42S<br>with window | QFC48<br>with window |                                                      |  |

| LC66P308                  | 42          | OTPROM 8 KB            | 512 W        | DIP42S                | QFP48E               |                                                      |  |

| LC66E408                  | 42          | EPROM 8 KB             | 512 W        | DIC42S<br>with window | QFC48<br>with window | Window and OTP evaluation versions                   |  |

| LC66P408                  | 42          | OTPROM 8 KB            | 512 W        | DIP42S                | QFP48E               | - 4.5 to 5.5 V/0.92 μs                               |  |

| LC66E516                  | 64          | EPROM 16 KB            | 512 W        | DIC64S<br>with window | QFC64<br>with window | -                                                    |  |

| LC66P516                  | 64          | OTPROM 16 KB           | 512 W        | DIP64S                | QFP64E               |                                                      |  |

| LC66E2108                 | 30          | EPROM 8 KB             | 384 W        |                       |                      |                                                      |  |

| LC66E2316                 | 42          | EPROM 16 KB            | 512 W        | DIC42S<br>with window | QFC48<br>with window | Mindow and address and                               |  |

| LC66E2516                 | 64          | EPROM 16 KB            | 512 W        | DIC64S<br>with window | QFC64<br>with window | Window evaluation versions<br>4.5 to 5.5 V/0.92 μs   |  |

| LC66E5316                 | 52/48       | EPROM 16 KB            | 512 W        | DIC52S<br>with window | QFC48<br>with window |                                                      |  |

| LC66P2108                 | 30          | OTPROM 8 KB            | 384 W        | DIP30SD               | MFP30S               |                                                      |  |

| LC66P2316                 | 42          | OTPROM 16 KB           | 512 W        | DIP42S                | QFP48E               | ОТР                                                  |  |

| LC66P2516                 | 64          | OTPROM 16 KB           | 512 W        | DIP64S                | QFP64E               | 4.0 to 5.5 V/0.95 μs                                 |  |

| LC66P5316                 | 48          | OTPROM 16 KB           | 512 W        | DIP48S                | QFP48E               | 1                                                    |  |

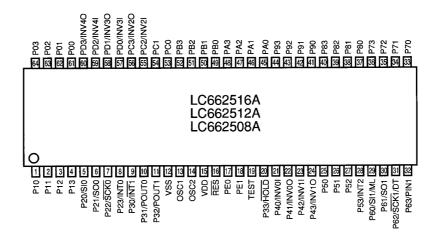

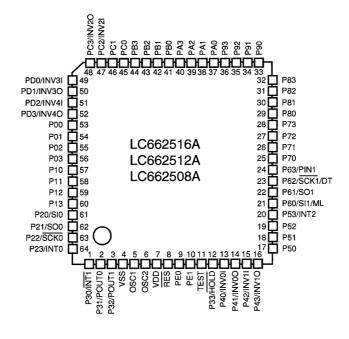

#### **Pin Assignments**

#### DIP64S

#### QFP64E

Top view

We recommend the use of reflow-soldering techniques to solder-mount QFP packages.

Please consult with your Sanyo representative for details on process conditions if the package itself is to be directly immersed in a dip-soldering bath (dip-soldering techniques).

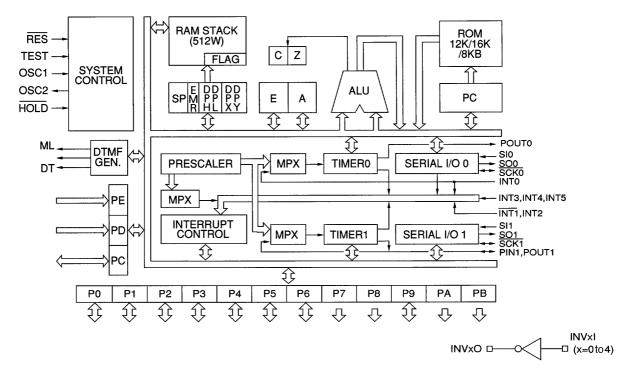

#### **System Block Diagram**

- When DT, ML, and DP are used, only the SIO channel can be used for serial I/O.

- The INT3, INT4, and INT5 pins can be used with internal functions.

#### Differences between the LC665XX Series and the LC6625XX Series

| Item                                                                                                  | LC6650XB Series<br>(Including the LC66599 evaluation chip)                                           | LC6655XB Series                                                                                              | LC6625XX Series                                                             |

|-------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| System differences  • Hardware wait time (number of cycles) when hold mode is cleared                 | 65536 cycles<br>About 64 ms at 4 MHz (Tcyc = 1 μs)                                                   | 16384 cycles<br>About 16 ms at 4 MHz (Tcyc = 1 µs)                                                           | 16384 cycles<br>About 16 ms at 4 MHz (Tcyc = 1 μs)                          |

| Value of timer 0 after a reset<br>(Including the value after hold mode<br>is cleared)                 | Set to FF0.                                                                                          | Set to FFC.                                                                                                  | Set to FFC.                                                                 |

| DTMF generator                                                                                        | None (Tools are handled with external devices.)                                                      | None                                                                                                         | Yes                                                                         |

| Inverter array                                                                                        | None (Tools are handled with external devices.)                                                      | None                                                                                                         | Yes                                                                         |

| Three-value inputs/comparator inputs                                                                  | Yes                                                                                                  | Yes                                                                                                          | None                                                                        |

| Three-state output from P31 and P32                                                                   | None                                                                                                 | None                                                                                                         | Yes                                                                         |

| Using P0 to clear halt mode                                                                           | In 4-bit groups                                                                                      | In 4-bit groups                                                                                              | Can be specified for each bit.                                              |

| External extended interrupts                                                                          | For INT3, INT4, and INT5.<br>(Tools are handled with external<br>devices.)                           | For INT3, INT4, and INT5.                                                                                    | INT3, INT4, and INT5 can be used with the internal functions.               |

| INT2 functions                                                                                        | Shared with P90 (INT2) (Tools are handled with external devices.)                                    | Shared with P90 (INT2)                                                                                       | Shared with P53 (INT2)                                                      |

| Differences in main characteristics • Operating power-supply voltage and operating speed (cycle time) | LC66506B/08B/12B/16B     4.0 to 6.0 V/0.92 to 10 μs     LC66E516/P516     4.5 to 5.5 V/0.92 to 10 μs | • 3.0 to 5.5 V/0.92 to 10 µs<br>• LC6655XA, 56XA<br>2.2 to 5.5 V/3.92 to 10 µs<br>3.0 to 5.5 V/1.96 to 10 µs | 3.0 to 5.5 V/0.95 to 10 μs                                                  |

| Pull-up resistors                                                                                     | P0, P1, P4, and P5: about 3 to 10 kΩ                                                                 | P0, P1, P4, and P5: about 3 to 10 k $\Omega$                                                                 | P0, P1, P4, and P5: about 100 kΩ                                            |

| Port voltage handling                                                                                 | P2, P3, P6, P7, and PA: 15V handling Others: Normal voltage                                          | P2, P3, P6, P7, and PA: 15V handling Others: Normal voltage                                                  | P2, P3, P61, P63, and PA:<br>15V voltage handling<br>Others: normal voltage |

## **Pin Function Overview**

| Pin                                              | I/O | Overview                                                                                                                                                                                                                                                                                                                                                                                                      | Output driver type                                                                                                                        | Options                                                             | State after a reset                        | Standby mode operation                                                                                      |

|--------------------------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|--------------------------------------------|-------------------------------------------------------------------------------------------------------------|

| P00<br>P01<br>P02<br>P03                         | I/O | <ul> <li>I/O ports P00 to P03</li> <li>Input or output in 4-bit or 1-bit units</li> <li>P00 to P03 support the halt mode control function (This function can be specified in bit units.)</li> </ul>                                                                                                                                                                                                           | Pch: Pull-up MOS type Nch: Intermediate sink current type                                                                                 | Pull-up MOS or<br>Nch OD output Output level on<br>reset            | High or low<br>(option)                    | Hold mode:<br>Output off<br>Halt mode:<br>Output<br>retained                                                |

| P10<br>P11<br>P12<br>P13                         | I/O | I/O ports P10 to P13 Input or output in 4-bit or 1-bit units                                                                                                                                                                                                                                                                                                                                                  | Pch: Pull-up MOS type Nch: Intermediate sink current type                                                                                 | Pull-up MOS or<br>Nch OD output     Output level on<br>reset        | High or low<br>(option)                    | Hold mode:<br>Output off<br>Halt mode:<br>Output<br>retained                                                |

| P20/SI0<br>P21/SO0<br>P22/SCK0<br>P23/INT0       | I/O | I/O ports P20 to P23 Input or output in 4-bit or 1-bit units P20 is also used as the serial input SI0 pin. P21 is also used as the serial output SO0 pin. P22 is also used as the serial clock SCK0 pin. P23 is also used as the INT0 interrupt request pin, and also as the timer 0 event counting and pulse width measurement input.                                                                        | Pch: CMOS type Nch: Intermediate sink current type Nch: +15V handling when OD option selected                                             | CMOS or Nch OD output                                               | н                                          | Hold mode:<br>Output off   Halt mode:<br>Output<br>retained                                                 |

| P30/INT1<br>P31/POUT0<br>P32/POUT1               | I/O | I/O ports P30 to P32 Input or output in 3-bit or 1-bit units P30 is also used as the INT1 interrupt request. P31 is also used for the square wave output from timer 0. P32 is also used for the square wave and PWM output from timer 1. P31 and P32 also support 3-state outputs.                                                                                                                            | Pch: CMOS type Nch: Intermediate sink current type Nch: +15V handling when OD option selected  Pch: +05V handling when OD option selected | CMOS or Nch OD output                                               | н                                          | Hold mode:<br>Output off<br>                                                                                |

| P33/HOLD                                         | ı   | Hold mode control input  Hold mode is set up by the HOLD instruction when HOLD is low. In hold mode, the CPU is restarted by setting HOLD to the high level. This pin can be used as input port P33 along with P30 to P32. When the P33/HOLD pin is at the low level, the CPU will not be reset by a low level on the RES pin. Therefore, applications must not set P33/HOLD low when power is first applied. |                                                                                                                                           |                                                                     |                                            |                                                                                                             |

| P40/INV0I<br>P41/INV0O<br>P42/INV1I<br>P43/INV1O | I/O | I/O ports P40 to P43 Input or output in 4-bit or 1-bit units Input or output in 8-bit units when used in conjunction with P50 to P53. Can be used for output of 8-bit ROM data when used in conjunction with P50 to P53. Dedicated inverter circuit (option)                                                                                                                                                  | Pch: Pull-up MOS type CMOS type when the inverter circuit option is selected Nch: Intermediate sink current type                          | Pull-up MOS or Nch OD output Output level on reset Inverter circuit | High or low<br>or inverter<br>I/O (option) | Hold mode: Port output off, inverter output off  Halt mode: Port output retained, inverter output continues |

Continued from preceding page.

| Pin                                                    | I/O | Overview                                                                                                                                                                                                                                                                                                                        | Output driver type                                                                                                                                                              | Options                                                                                                                      | State after a reset                 | Standby mode operation                                                                                   |

|--------------------------------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|----------------------------------------------------------------------------------------------------------|

| P50<br>P51<br>P52<br>P53/INT2                          | I/O | I/O ports P50 to P53 Input or output in 4-bit or 1-bit units Input or output in 8-bit units when used in conjunction with P40 to P43. Can be used for output of 8-bit ROM data when used in conjunction with P40 to P43. P53 is also used as the INT2 interrupt request.                                                        | Pch: Pull-up MOS type Nch: Intermediate sink current type                                                                                                                       | Pull-up MOS or<br>Nch OD output Output level on<br>reset                                                                     | High or low<br>(option)             | Hold mode:<br>Output off<br>                                                                             |

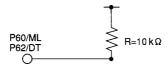

| P60/SI1/ML<br>P61/S01/<br>P62/<br>SCK1/DT/<br>P63/PIN1 | I/O | I/O ports P60 to P63 Input or output in 4-bit or 1-bit units P60 is also used as the SI1 serial input pin and as the ML melody output pin. P61 is also used as the SO1 serial output pin. P62 is also used as the SCK1 serial clock pin and the DT dial tone output pin. P63 is also used for the event count input to timer 1. | Pch: CMOS type Nch: Intermediate sink current type Nch: +15V handling when OD option selected (P61 and P63 only)  Nch: +15V handling when OD option selected (P61 and P63 only) | CMOS or Nch OD output (When the ML or DT output is used, select open-drain output and provide an external pull-up resistor.) | н                                   | Hold mode:<br>Output off<br>Halt mode:<br>Output<br>retained                                             |

| P70<br>P71<br>P72<br>P73                               | 0   | Output ports P70 to P73  Output in either 1-bit or 4-bit units.  The contents of the output latch are input by input instruction.                                                                                                                                                                                               | Pch: Pu MOS     Nch: Intermediate sink current type                                                                                                                             | Pull-up MOS or Nch<br>OD output                                                                                              | н                                   | Hold mode:<br>Output off<br>Halt mode:<br>Output<br>retained                                             |

| P80<br>P81<br>P82<br>P83                               | 0   | Output ports P80 to P83  Output in either 1-bit or 4-bit units. The contents of the output latch are input by input instruction.                                                                                                                                                                                                | Pch: Pu MOS Nch: Intermediate sink current type                                                                                                                                 | CMOS or Pch OD output     Output level on reset                                                                              | High or low<br>(option)             | Hold mode:<br>Output off<br>Halt mode:<br>Output<br>retained                                             |

| P90<br>P91<br>P92<br>P93                               | I/O | I/O ports P90 to 93.  • Input or output in either 1-bit or 4-bit units.                                                                                                                                                                                                                                                         | Pch: CMOS Nch: Intermediate sink current type                                                                                                                                   | CMOS or Nch OD output                                                                                                        | н                                   | Hold mode:<br>Output off<br>Halt mode:<br>Output<br>retained                                             |

| PA0<br>PA1<br>PA2<br>PA3                               | 0   | Output ports PA0 to PA3  Output in either 1-bit or 4-bit units.  The contents of the output latch are input by input instruction.                                                                                                                                                                                               | Pch: Pu MOS     Nch: +15-V handling when     OD option selected                                                                                                                 | Pull-up MOS or Nch<br>OD output                                                                                              | н                                   | Hold mode:<br>Output off<br>Halt mode:<br>Output<br>retained                                             |

| PB0<br>PB1<br>PB2<br>PB3                               | 0   | Output ports PB0 to PB3  Output in either 1-bit or 4-bit units.  The contents of the output latch are input by input instruction.                                                                                                                                                                                               | Pch: Pull-up MOS Nch: Intermediate sink current type                                                                                                                            | Pull-up MOS or Nch<br>OD output                                                                                              | н                                   | Hold mode:<br>Output off<br>Halt mode:<br>Output<br>retained                                             |

| PC0<br>PC1<br>PC2/INV2I<br>PC3/INV2O                   | I/O | I/O ports PC0 to PC3  • Output in either 1-bit or 4-bit units.  • Dedicated input ports PC2 to PC3  • Dedicated inverter circuits (option)                                                                                                                                                                                      | Pch: CMOS Nch: Intermediate sink current type                                                                                                                                   | CMOS or Nch OD output     Inverter circuit                                                                                   | High or<br>inverter I/O<br>(option) | Hold mode: Port output off Inverter output off  Halt mode: Port output retained Inverter output retained |

Continued from preceding page.

| Pin                                              | I/O | Overview                                                                                                                  | Output driver type                                                                                       | Options                                              | State after a reset                            | Standby mode operation                                            |

|--------------------------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|------------------------------------------------------|------------------------------------------------|-------------------------------------------------------------------|

| PD0/INV3I<br>PD1/INV3O<br>PD2/INV4I<br>PD3/INV4O | I   | Dedicated input ports PD0 to PD3<br>Dedicated inverter circuits (option)                                                  | When the inverter circuit option is selected.     Pch: CMOS type     Nch: Intermediate sink current type | Inverter circuits                                    | Normal<br>input or<br>inverter I/O<br>(option) | Inverter  • Hold mode: output off  • Halt mode: output continues  |

| PE0<br>PE1                                       | I   | Dedicated input ports                                                                                                     |                                                                                                          |                                                      |                                                | Hold mode:<br>input<br>disabled<br>Halt mode:<br>input<br>enabled |

| OSC1                                             | 0   | System clock oscillator connections When an external clock is used, leave OSC2 open and connect the clock signal to OSC1. |                                                                                                          | Ceramic oscillator<br>or external clock<br>selection | Option<br>selection                            | Hold mode: Oscillator stops Halt mode: Oscillator continues       |

| RES                                              | I   | System reset input When the P33/HOLD pin is at the high level, a low level input to the RES pin will initialize the CPU.  |                                                                                                          |                                                      |                                                |                                                                   |

| TEST                                             | I   | CPU test pin This pin must be connected to V <sub>SS</sub> during normal operation.                                       |                                                                                                          |                                                      |                                                |                                                                   |

| V <sub>DD</sub><br>V <sub>SS</sub>               |     | Power supply pins                                                                                                         |                                                                                                          |                                                      |                                                |                                                                   |

Note: Pull-up MOS type: The output circuit includes a MOS transistor that pulls the pin up to  $V_{\text{DD}}$ .

CMOS output: Complementary output.

OD output: Open-drain output

## **User Options**

1. Ports 0, 1, 4, 5, and 8 output level at reset option

The output levels at reset for I/O ports 0, 1, 4, 5, and 8 in independent 4-bit groups, can be selected from the following two options.

| Option               | Conditions and notes                                       |

|----------------------|------------------------------------------------------------|

| Output high at reset | The four bits of ports 0, 1, 4, 5, or 8 are set in a group |

| Output low at reset  | The four bits of ports 0, 1, 4, 5, or 8 are set in a group |

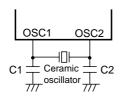

# 2. Oscillator circuit options

• Main clock

| Option             | Circuit                             | Conditions and notes                  |

|--------------------|-------------------------------------|---------------------------------------|

| External clock     | OSC1                                | The input has Schmitt characteristics |

| Ceramic oscillator | C1 OSC1  Ceramic oscillator C2 OSC2 |                                       |

Note: There is no RC oscillator option.

#### 3. Watchdog timer option

A runaway detection function (watchdog timer) can be selected as an option.

## 4. Port output type options

• The output type of each bit (pin) in ports P0, P1, P2, P3 (except for the P33/HOLD pin), P4, P5, P6, P7, P9, PA, PB, and PC can be selected individually from the following two options. (in1-bit units)

| Option                                | Circuit                 | Conditions and notes                                                                                                                                                                                                                                     |

|---------------------------------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Open-drain output                     | Output data  Input data | The ports P2, P3, P5, P6, and P9 inputs have Schmitt characteristics. P7, PA, and PB are output-only ports.                                                                                                                                              |

| Output with built-in pull-up resistor | Output data  DSB        | The ports P2, P3, P5, P6, and P9 inputs have Schmitt characteristics.  The CMOS outputs (ports P2, P3, P6, P9, and PC) and the pull-up MOS outputs (P0, P1, P4, P5, P7, PA, and PB) are distinguished by the drive capacity of the p-channel transistor. |

• The two options can be specified for P8 (in 1-bit units)

| Option                                              | Circuit          | Conditions and notes |

|-----------------------------------------------------|------------------|----------------------|

| Open-drain output                                   | Output data      |                      |

| Output with built-in pull-up resistor (CMOS output) | Output data  DSB |                      |

# 5. Inverter array circuit option

One of the following options can be selected for each of the following port sets: P40/P41, P42/P43, PC2/PC3, PD0/PD1, and PD2/PD3. (PDs do not use option 1 because they are dedicated to input.)

| Option                  | Circuit                                                                                           | Conditions and notes                                                                                                                                                                    |

|-------------------------|---------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                         | Output data  Input data                                                                           | When the open-drain output type is selected                                                                                                                                             |

| Normal port I/O circuit | Output data    DSB                                                                                | When the built-in pull-up resistor output type is selected. The CMOS outputs (PC) and the pull-up MOS outputs (P4) are distinguished by the drive capacity of the P-channel transistor. |

| Inverter I/O circuit    | Output data high Input data  Output data  Output data  DSB  Output data  Output data  Output data | If this option is selected, The I/O circuit is disabled by the DSB signal. Also note that the open-drain port output type option and the high level at reset option must be selected.   |

# LC662516 Series Option Data Area and Definitions

| ROM area | Bit |            | Option specified      | Option/data relationship                   |  |  |

|----------|-----|------------|-----------------------|--------------------------------------------|--|--|

|          | 7   | P5         | Output level at reset | 0 = high level, 1 = low level              |  |  |

|          | 6   | P4         | Output level at reset | 0 - High level, 1 - low level              |  |  |

|          | 5 U |            |                       | This bit must be set to 0.                 |  |  |

| 3FF0H    | 4   | Oscillator | option                | 0 = external clock, 1 = ceramic oscillator |  |  |

| 0.70.7   | 3   | P8         |                       |                                            |  |  |

|          | 2   | P1         | Output level at reset | 0 = low level, 1 = high level              |  |  |

|          | 1   | P0         |                       |                                            |  |  |

|          | 0   |            | g timer option        | 0 = none, 1 = yes                          |  |  |

|          | 7   | P13        |                       |                                            |  |  |

|          | 6   | P12        | Output type           | 0 = OD, 1 = PU                             |  |  |

|          | 5   | P11        |                       |                                            |  |  |

| 3FF1H    | 4   | P10<br>P03 |                       |                                            |  |  |

|          |     |            |                       |                                            |  |  |

|          | 1   | P02<br>P01 | Output type           | 0 = OD, 1 = PU                             |  |  |

|          | 0   | P00        |                       |                                            |  |  |

|          | 7   | Unused     |                       | This bit must be set to 0.                 |  |  |

|          | 6   | P32        |                       | This bit must be set to e.                 |  |  |

|          | 5   | P31        | Output type           | 0 = OD, 1 = PU                             |  |  |

|          | 4   | P30        | 3                     |                                            |  |  |

| 3FF2H    | 3   | P23        |                       |                                            |  |  |

|          | 2   | P22        | _                     |                                            |  |  |

|          | 1   | P21        | Output type           | 0 = OD, 1 = PU                             |  |  |

|          | 0   | P20        |                       |                                            |  |  |

|          | 7   | P53        |                       |                                            |  |  |

|          | 6   | P52        | Output type           | 0 = OD, 1 = PU                             |  |  |

|          | 5   | P51        | Output type           | 0 = OD, 1 = PO                             |  |  |

| 3FF3H    | 4   | P50        |                       |                                            |  |  |

| 311311   | 3   | P43        |                       |                                            |  |  |

|          | 2   | P42        | Output type           | 0 = OD, 1 = PU                             |  |  |

|          | 1   | P41        |                       |                                            |  |  |

|          | 0   | P40        |                       |                                            |  |  |

|          | 7   | P73        |                       |                                            |  |  |

|          | 6   | P72        | Output type           | 0 = OD, 1 = PU                             |  |  |

|          | 5   | P71        |                       |                                            |  |  |

| 3FF4H    | 4   | P70        |                       |                                            |  |  |

|          | 3   | P63        |                       |                                            |  |  |

|          | 2   | P62<br>P61 | Output type           | 0 = OD, 1 = PU                             |  |  |

|          | 0   | P60        | 1                     |                                            |  |  |

|          | 7   | P93        |                       |                                            |  |  |

|          | 6   | P92        | 1                     |                                            |  |  |

|          | 5   | P91        | Output type           | 0 = OD, 1 = PU                             |  |  |

|          | 4   | P90        |                       |                                            |  |  |

| 3FF5H    | 3   | P83        |                       |                                            |  |  |

|          | 2   | P82        | 0.47-44-7-            | 0.004.84                                   |  |  |

|          | 1   | P81        | Output type           | 0 = OD, 1 = PU                             |  |  |

|          | 0   | P80        |                       |                                            |  |  |

|          | 7   | PB3        |                       |                                            |  |  |

|          | 6   | PB2        | Output type           | 0 = OD, 1 = PU                             |  |  |

|          | 5   | PB1        | - Sample type         | 0 - 00, 1 - 10                             |  |  |

| 3FF6H    | 4   | PB0        |                       |                                            |  |  |

| ]        | 3   | PA3        |                       |                                            |  |  |

|          | 2   | PA2        | Output type           | 0 = OD, 1 = PU                             |  |  |

|          | 1   | PA1        |                       | ·                                          |  |  |

|          | 0   | PA0        |                       |                                            |  |  |

Continued from preceding page.

| ROM area   Bit                                                                                                                                                                          |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SFFH                                                                                                                                                                                    |  |

| 3   PC3   2   PC2   1   PC1   0   0   0   0   0   0   0   0   0                                                                                                                         |  |

| 3                                                                                                                                                                                       |  |

| 3 PC3 2 PC2 1 PC1 0 PC2 1 1 PC1 0 PC2 7 ML disabled option                                                                                                                              |  |

| 1                                                                                                                                                                                       |  |

| 1                                                                                                                                                                                       |  |

| 7                                                                                                                                                                                       |  |

| SFFBH                                                                                                                                                                                   |  |

| S                                                                                                                                                                                       |  |

| 3FF8H                                                                                                                                                                                   |  |

| 3                                                                                                                                                                                       |  |

| 2   PC3                                                                                                                                                                                 |  |

| 1                                                                                                                                                                                       |  |

| O P41                                                                                                                                                                                   |  |

| This bit must be set to 0.   This bit must be set to 0.                                                                                                                                 |  |

| 3FF9H                                                                                                                                                                                   |  |

| 3                                                                                                                                                                                       |  |

| 3                                                                                                                                                                                       |  |

| 3                                                                                                                                                                                       |  |

| 1                                                                                                                                                                                       |  |

| 3FFAH  1 0 7 6 5 Unused  2 1 Unused  7 6 0 5 This bit must be set to 0.  This bit must be set to 0. |  |

| 7   6                                                                                                                                                                                   |  |

| 3                                                                                                                                                                                       |  |

| 3                                                                                                                                                                                       |  |

| 3FFAH  3 2 Unused  7 6 5 4 3 Unused  This bit must be set to 0.  This bit must be set to 0.                                                                                             |  |

| 3                                                                                                                                                                                       |  |

| 2                                                                                                                                                                                       |  |

| This bit must be set to 0.                                              |  |

| 7 6 Unused This bit must be set to 0.  3FFBH 3 2 Unused This bit must be set to 0.                                                                                                      |  |

| 3FFBH This bit must be set to 0.  This bit must be set to 0.  This bit must be set to 0.                                                                                                |  |

| 3FFBH This bit must be set to 0.  This bit must be set to 0.  This bit must be set to 0.                                                                                                |  |

| 3FFBH 2 Unused This bit must be set to 0.  This bit must be set to 0.  This bit must be set to 0.                                                                                       |  |

| 3FFBH 4 3 2 Unused This bit must be set to 0.                                                                                                                                           |  |

| 3 2 Unused This bit must be set to 0.                                                                                                                                                   |  |

| 2 Unused This bit must be set to 0.                                                                                                                                                     |  |

| Unused This bit must be set to 0.                                                                                                                                                       |  |

|                                                                                                                                                                                         |  |

| 0                                                                                                                                                                                       |  |

| 7                                                                                                                                                                                       |  |

| 6 Unused This bit must be set to 0.                                                                                                                                                     |  |

| 5                                                                                                                                                                                       |  |

| 3FFCH 4                                                                                                                                                                                 |  |

| 3                                                                                                                                                                                       |  |

| Unused This bit must be set to 0.                                                                                                                                                       |  |

|                                                                                                                                                                                         |  |

| 7                                                                                                                                                                                       |  |

|                                                                                                                                                                                         |  |

| 5                                                                                                                                                                                       |  |

| This data is generated by the generated                                                                                                                                                 |  |

| 3FFDH Reserved. Must be set to predefined data values.  Reserved. Must be set to predefined data values.  If the assembler is not used, set this data to 00.                            |  |

|                                                                                                                                                                                         |  |

| 1                                                                                                                                                                                       |  |

| 0                                                                                                                                                                                       |  |

Continued from preceding page.

| ROM area | Bit | Option specified                                 | Option/data relationship                           |  |  |

|----------|-----|--------------------------------------------------|----------------------------------------------------|--|--|

|          | 7   |                                                  |                                                    |  |  |

|          | 6   |                                                  |                                                    |  |  |

|          | 5   |                                                  |                                                    |  |  |

| 3FFEH    | 4   | Reserved. Must be set to predefined data values. | This data is generated by the assembler.           |  |  |

| SFFER    | 3   | Reserved. Must be set to predefined data values. | If the assembler is not used, set this data to 00. |  |  |

|          | 2   |                                                  |                                                    |  |  |

|          | 1   |                                                  |                                                    |  |  |

|          | 0   |                                                  |                                                    |  |  |

|          | 7   |                                                  |                                                    |  |  |

|          | 6   | Reserved. Must be set to predefined data values. |                                                    |  |  |

|          | 5   |                                                  |                                                    |  |  |

| 3FFFH    | 4   |                                                  | This data is generated by the assembler.           |  |  |

| 311111   | 3   |                                                  | If the assembler is not used, set this data to 00. |  |  |

|          | 2   |                                                  |                                                    |  |  |

|          | 1   |                                                  |                                                    |  |  |

|          | 0   |                                                  |                                                    |  |  |

# **Specifications**

## Absolute Maximum Ratings at Ta = 25°C, $V_{SS} = 0$ V

| Parameter                   | Symbol              | Conditions                                                                                                | Ratings                       | Unit | Note |

|-----------------------------|---------------------|-----------------------------------------------------------------------------------------------------------|-------------------------------|------|------|

| Maximum supply voltage      | V <sub>DD</sub> max | V <sub>DD</sub>                                                                                           | -0.3 to +7.0                  | V    |      |

| Input voltage               | V <sub>IN</sub> 1   | P2, P3 (except for the P33/HOLD pin),<br>P61, and P63                                                     | -0.3 to +15.0                 | V    | 1    |

|                             | V <sub>IN</sub> 2   | All other inputs                                                                                          | $-0.3$ to $V_{DD} + 0.3$      | V    | 2    |

| Output voltage              | V <sub>OUT</sub> 1  | P2, P3 (except for the P33/HOLD pin),<br>P61, P63, and PA                                                 | -0.3 to +15.0                 | V    | 1    |

|                             | V <sub>OUT</sub> 2  | All other inputs                                                                                          | -0.3 to V <sub>DD</sub> + 0.3 | V    | 2    |

|                             | I <sub>ON</sub> 1   | P0, P1, P2, P3 (except for the P33/ <del>HOLD</del> pin),<br>P4, P5, P6, P7, P8, P9, PA, PB, PC, PD1, PD3 | 20                            | mA   | 3    |

|                             | I <sub>ON</sub> 2   | P41, P43, PC3, PD1, PD3                                                                                   | 20                            | mA   | 3    |

| Output current per pin      | -l <sub>OP</sub> 1  | P0, P1, P4, P5, P7, PA, PB                                                                                | 2                             | mA   | 4    |

|                             | -I <sub>OP</sub> 2  | P2, P3 (except for the P33/HOLD pin), P6, P8, P9, and PC                                                  | 4                             | mA   | 4    |

|                             | -I <sub>OP</sub> 3  | P41, P43, PC3, PD1, PD3                                                                                   | 10                            | mA   | 4    |

|                             | ΣI <sub>ON</sub> 1  | P0, P1, P2, P3 (except for the P33/HOLD pin), PB, PC, and PD                                              | 75                            | mA   | 3    |

| Tatal air arment            | ΣI <sub>ON</sub> 2  | P4, P5, P6, P7, P8, P9, and PA                                                                            | 75                            | mA   | 3    |

| Total pin current           | Σ I <sub>OP</sub> 1 | P0, P1, P2, P3 (except for the P33/HOLD pin), PB, PC, and PD                                              | 25                            | mA   | 4    |

|                             | ΣI <sub>OP</sub> 2  | P4, P5, P6, P7, P8, P9, and PA                                                                            | 25                            | mA   | 4    |

| Allowable power dissipation | Pd max              | Ta = -30 to +70°C: DIP64S (QFP64E)                                                                        | 600 (430)                     | mW   | 5    |

| Operating temperature       | Topr                |                                                                                                           | -30 to +70                    | °C   |      |

| Storage temperature         | Tstg                |                                                                                                           | -55 to +125                   | °C   |      |

Note: 1. Applies to pins with open-drain output specifications. For pins with other than open-drain output specifications, the ratings in the pin column for that pin apply.

- 2. For the oscillator input and output pins, levels up to the free-running oscillation level are allowed.

- 3. Sink current (Applies to P8 when the CMOS output specifications and applies to PD when the inverter array specifications are selected.)

- 4. Source current (Applies to all pins except P8 for which the pull-up output specifications, the CMOS output specifications, or the inverter array specifications have been selected. Applies to PD pins for which the inverter array specifications have been selected.)

Contact your Sanyo representative for details on the electrical characteristics when the inverter array specifications option is selected.

- 5. We recommend the use of reflow soldering techniques to solder mount QFP packages. Please consult with your Sanyo representative for details on process conditions if the package itself is to be directly immersed in a dip-soldering bath (dip-soldering techniques).

# Allowable Operating Ranges at Ta = -30 to $+70^{\circ}C$ , $V_{SS} = 0$ V, $V_{DD} = 3.0$ to 5.5 V, unless otherwise specified.

| Parameter                                    | Symbol                                | Conditions                                                                                                                                               | min                 | typ | max                 | Unit        | Note |

|----------------------------------------------|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----|---------------------|-------------|------|

| Operating supply voltage                     | V <sub>DD</sub>                       | V <sub>DD</sub>                                                                                                                                          | 3.0                 |     | 5.5                 | V           |      |

| Memory retention supply voltage              | V <sub>DD</sub> H                     | V <sub>DD</sub> : During hold mode                                                                                                                       | 1.8                 |     | 5.5                 | V           |      |

|                                              | V <sub>IH</sub> 1                     | P2, P3 (except for the P33/HOLD pin),<br>P61, and P63: N-channel output transistor off                                                                   | 0.8 V <sub>DD</sub> |     | 13.5                | V           | 1    |

| Input high-level voltage                     | V <sub>IH</sub> 2                     | P33/HOLD, P5, P60, P62, P9, RES, OSC1:<br>N-channel output transistor off                                                                                | 0.8 V <sub>DD</sub> |     | V <sub>DD</sub>     | V           | 2    |

|                                              | V <sub>IH</sub> 3                     | P0, P1, P4, P5, PC, PD, PE:<br>N-channel output transistor off                                                                                           | 0.8 V <sub>DD</sub> |     | V <sub>DD</sub>     | ٧           | 3    |

|                                              | V <sub>IL</sub> 1                     | P2, P3 (except for the P33/HOLD pin), P5, P6, P9, RES, and OSC1: N-channel output transistor off                                                         | V <sub>SS</sub>     |     | 0.2 V <sub>DD</sub> | V           | 2    |

| Input low-level voltage                      | V <sub>IL</sub> 2                     | P33/HOLD: V <sub>DD</sub> = 1.8 to 5.5 V                                                                                                                 | V <sub>SS</sub>     |     | 0.2 V <sub>DD</sub> | V           |      |

|                                              | V <sub>IL</sub> 3                     | P0, P1, P4, P5, PC, PD, PE, TEST:<br>N-channel output transistor off                                                                                     | V <sub>SS</sub>     |     | 0.2 V <sub>DD</sub> | ٧           | 3    |

| Operating frequency (instruction cycle time) | fop<br>(Tcyc)                         |                                                                                                                                                          | 0.4<br>(10)         |     | 4.2<br>(0.95)       | MHz<br>(µs) |      |

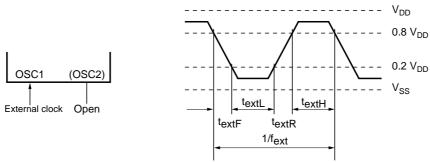

| [External clock input conditions]            |                                       |                                                                                                                                                          |                     |     |                     |             |      |

| Frequency                                    | f <sub>ext</sub>                      | OSC1: Defined by Figure 1. Input the clock signal to OSC1 and leave OSC2 open. (External clock input must be selected as the oscillator circuit option.) | 0.4                 |     | 4.2                 | MHz         |      |

| Pulse width                                  | t <sub>extH</sub> , t <sub>extL</sub> | OSC1: Defined by Figure 1. Input the clock signal to OSC1 and leave OSC2 open. (External clock input must be selected as the oscillator circuit option.) | 100                 |     |                     | ns          |      |

| Rise and fall times                          | t <sub>extR</sub> , t <sub>extF</sub> | OSC1: Defined by Figure 1. Input the clock signal to OSC1 and leave OSC2 open. (External clock input must be selected as the oscillator circuit option.) |                     |     | 30                  | ns          |      |

Note: 1. Applies to pins with open-drain specifications. However,  $V_{IH}2$  applies to the P33/ $\overline{HOLD}$  pin. When ports P2, P3, and P6 have CMOS output specifications they cannot be used as input pins.

Applies to pins with open-drain specifications. P9 port pins with CMOS output specifications cannot be used as input pins.

PC port pins with CMOS output specifications cannot be used as input pins.

Contact Sanyo for details on the allowable operating ranges for P4,PC, and PD pins with inverter array specifications.

# Electrical Characteristics at Ta = -30 to +70 $^{\circ}C,\,V_{SS}$ = 0 V, $V_{DD}$ = 3.0 to 5.5 V unless otherwise specified.

| Parameter                    |          | Symbol                              | Conditions                                                                                                                                          | min                   | typ                 | max                 | Unit | Note |

|------------------------------|----------|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|---------------------|---------------------|------|------|

| Input high-level current     |          | I <sub>IH</sub> 1                   | P2, P3 (except for the P33/HOLD pin),<br>P61, and P63: V <sub>IN</sub> = 13.5 V, with the output<br>Nch transistor off                              |                       |                     | 5.0                 | μA   | 1    |

|                              |          | I <sub>IH</sub> 2                   | P0, P1, P4, P5, P6, P9, PC, TEST, RES, and P33/HOLD (Does not apply to P61 and P63.): $V_{\rm IN} = V_{\rm DD},$ with the output Nch transistor off |                       |                     | 1.0                 | μA   | 1    |

|                              |          | I <sub>IH</sub> 3                   | PD, PE: V <sub>IN</sub> = V <sub>DD</sub> ,<br>with the output Nch transistor off                                                                   |                       |                     | 1.0                 | μA   | 1    |

| leavet level average         |          | I <sub>IL</sub> 1                   | Input ports other than PD and PE3: V <sub>IN</sub> = V <sub>SS</sub> , with the output Nch transistor off                                           | -1.0                  |                     |                     | μΑ   | 2    |

| Input low-level current      |          | I <sub>IL</sub> 2                   | PD, PE: V <sub>IN</sub> = V <sub>SS</sub> , with the output Nch transistor off                                                                      | -1.0                  |                     |                     | μA   | 2    |

| Output high lovel veltage    |          | \/ 1                                | P2, P3 (except for the P33/HOLD pin),<br>P6, P8, P9, and PC: I <sub>OH</sub> = -1 mA                                                                | V <sub>DD</sub> – 1.0 |                     |                     |      | 2    |

| Output high-level voltage    |          | V <sub>OH</sub> 1                   | P2, P3 (except for the P33/HOLD pin),<br>P6, P8, P9, and PC: I <sub>OH</sub> = -0.1 mA                                                              | V <sub>DD</sub> – 0.5 |                     |                     | - V  | 3    |

| Value of the output pull-up  | resistor | R <sub>PO</sub>                     | P0, P1, P4, P5, P7, PA, and PB                                                                                                                      | 30                    | 100                 | 300                 | kΩ   |      |

|                              |          | V <sub>OL</sub> 1                   | P0, P1, P2, P3, P4, P5, P6, P7, P8, P9, PA, PB, and PC (except for the P33/HOLD pin): I <sub>OL</sub> = 1.6 mA                                      |                       |                     | 0.4                 | V    | 5    |

| Output low-level voltage     |          | V <sub>OL</sub> 2                   | P0, P1, P2, P3, P4, P5, P6, P7, P8, P9, PA, PB, and PC (except for the P33/HOLD pin): I <sub>OL</sub> = 8 mA                                        |                       |                     | 1.5                 | V    | 5    |

|                              |          | I <sub>OFF</sub> 1                  | P2, P3, P61, P63, and PA: V <sub>IN</sub> = 13.5 V                                                                                                  |                       |                     | 5.0                 | μA   | 6    |

| Output off leakage curren    | t        | I <sub>OFF</sub> 2                  | Does not apply to P2, P3, P61, P63, P8, and PA: $V_{IN} = V_{DD}$                                                                                   |                       |                     | 1.0                 | μA   | 6    |

|                              |          | I <sub>OFF</sub> 3                  | P8: V <sub>IN</sub> = V <sub>SS</sub>                                                                                                               | -1.0                  |                     |                     | μA   | 7    |

| [Schmitt characteristics]    | L        |                                     |                                                                                                                                                     | 1                     |                     |                     |      |      |

| Hysteresis voltage           |          | V <sub>HYS</sub>                    | P2, P3, P5, P6, P61, P9, RES, OSC1 (EXT)                                                                                                            |                       | 0.1 V <sub>DD</sub> |                     | V    |      |

| High-level threshold volta   | ge       | Vt <sub>H</sub>                     |                                                                                                                                                     | 0.5 V <sub>DD</sub>   |                     | 0.8 V <sub>DD</sub> | V    |      |

| Low-level threshold voltage  | ge       | Vt L                                |                                                                                                                                                     | 0.2 V <sub>DD</sub>   |                     | 0.5 V <sub>DD</sub> | V    |      |

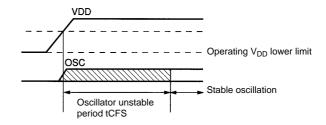

| [Ceramic oscillator]         | l        |                                     |                                                                                                                                                     | I                     |                     |                     |      | 1    |

| Oscillator frequency         |          | f <sub>CF</sub>                     | OSC1, OSC2: See Figure 2. 4 MHz                                                                                                                     |                       | 4.0                 |                     | MHz  |      |

| Oscillator stabilization tim | е        | f <sub>CFS</sub>                    | See Figure 3. 4 MHz                                                                                                                                 |                       |                     | 10.0                | ms   |      |

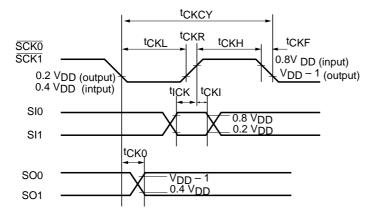

| [Serial clock]               |          |                                     |                                                                                                                                                     |                       |                     |                     |      | 1    |

| 0 1 0                        | Input    |                                     |                                                                                                                                                     | 0.9                   |                     |                     | μs   |      |

| Cycle time                   | Output   | t <sub>CKCY</sub>                   |                                                                                                                                                     | 2.0                   |                     |                     | Тсус |      |

| Low-level and high-level     | Input    | t <sub>CKL</sub>                    | SCK0, SCK1: With the timing of Figure 4 and the test load of Figure 5.                                                                              | 0.4                   |                     |                     | μs   |      |

| pulse widths                 | Output   | t <sub>CKH</sub>                    | The test load of Figure 5.                                                                                                                          | 1.0                   |                     |                     | Тсус |      |

| Rise an fall times Output    |          | t <sub>CKR</sub> , t <sub>CKF</sub> |                                                                                                                                                     |                       |                     | 0.1                 | μs   |      |

| [Serial input]               |          |                                     |                                                                                                                                                     |                       |                     |                     |      |      |

| Data setup time              |          | t <sub>ICK</sub>                    | SI0, SI1: With the timing of Figure 4.                                                                                                              | 0.3                   |                     |                     | μs   |      |

| Data hold time               |          | t <sub>CKI</sub>                    | Stipulated with respect to the rising edge (↑) of SCK0, SCK1.                                                                                       | 0.3                   |                     |                     | μs   |      |

| [Serial output]              | '        |                                     |                                                                                                                                                     |                       |                     |                     |      | •    |